Hi Snake, I was hoping you'd drop by at some point. Welcome to the forum.

The CSM stuff is news to me, though. I haven't really looked at this since 1997, when I was talking to Tatsuyuki Satoh (original MAME core, and the one I think Stef based his on) - he has some japanese documents which suggested CSM mode was useless without the timer interrupts. Timer A would do key ON, and you'd have to key it OFF again yourself in an interrupt. We tried to figure it out but I eventually decided it'd be pretty useless on the Genesis.

I get the feeling CSM is one of those functions that's probably implemented a little differently across a variety of chips, possibly even within the OPN line. Those documents he had may have been correct for another Yamaha chip. It would be nice to have a look at them, but I guess he never scanned them in.

The only thing (as far as I remember) that I still want to know is this: The YM2612 (apparently, and I don't remember where I found this) output DAC has one bit less than it would normally need. Something is done to remove one bit before it goes into the DAC. It appears to be some sort of compression/scaling which results in values close to silence being much louder. If you can figure that out I'd be very interested.

I think I know the answer to that one.

The YM2612 has an embedded YM3016 DAC. I know that for sure. I also obtained a datasheet for the YM3016 DAC when I got the YM2608 documentation, but unfortunately, the YM3016 datasheet is also in Japanese, and I haven't found an English version. Fortunately, that doesn't matter one bit, as I've noticed the YM3015 is

identical to the YM3016, with the exception that it takes a 12V input rather than the 5V input the YM3016 uses, and there's a YM3015 datasheet publically available in English. If you look at the datasheets, they contain the exact same information, with only the operating voltages differing.

Here's the YM3016 datasheet in Japanese:

http://nemesis.hacking-cult.org/MegaDri ... M3016J.pdf

and here's the YM3015 datasheet in English:

http://nemesis.hacking-cult.org/MegaDri ... YM3015.pdf

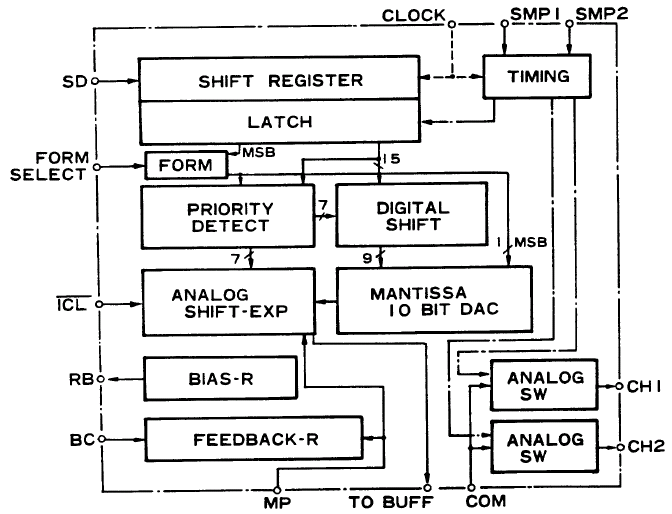

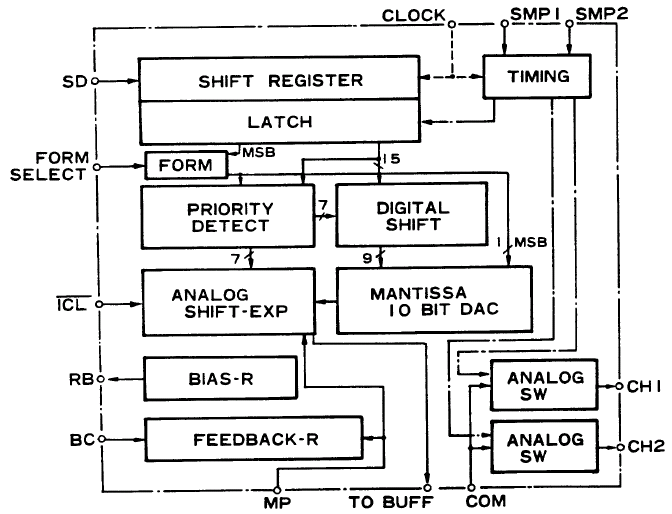

Many other DAC's in the YM301X line like the YM3012 and YM3014 take the input to the DAC in a floating point format, with a 3-bit exponent and a 10-bit mantissa. The YM3015 and YM3016 are different in that they take their input as a 16-bit integer value in either binary or 2's compliment form. Internally, the DAC still converts that 16-bit input into a 3-bit exponent and 10-bit mantissa before using it however. Looking at the YM3015 datasheet, here's a block diagram of the internal operations the DAC performs:

SD is the 16-bit serial data input, which comes from the accumulator in the case of the YM2612. The "Form Select" line switches between binary and 2's compliment mode. The "Form Select" and "ICL" lines are also tied to bits in the test register.

This internal conversion process means that although the output from the accumulator is 16-bit (with 14-bits of meaningful data from the operator unit), internally, the DAC converts it back to a 10-bit mantissa and 3-bit exponent before generating the analog output, so there is the potential for some loss of precision within the DAC unit. I haven't had a good look yet at the effects of the internal floating point conversion in the DAC on the precision of the signal output. There's also still a question in my mind about what the YM2612 sets the lower 2 bits of the 16-bit accumulator output to. They might not simply be 0.

I was going to look at the DAC last, once I've finished examining the other components of the YM2612. I've also noticed the extreme jump between low volume and silence though. I'm sure the answer to that behaviour lies in the DAC.